Editorials

Will Buldozer have the memory performance it needs?

- Details

- By Sean Kalinich

- Hits: 4007

Some specs on AMD’s next generation CPU Called Bulldozer have found their way on to the Internet. In what appears to be a conglomeration of leaked slides and other info from around the web. We took a look at some of this and compared it to what we know about AMD’s existing CPU architecture as well as what Intel has to offer with their Core line up.

Some specs on AMD’s next generation CPU Called Bulldozer have found their way on to the Internet. In what appears to be a conglomeration of leaked slides and other info from around the web. We took a look at some of this and compared it to what we know about AMD’s existing CPU architecture as well as what Intel has to offer with their Core line up.

First let’s talk about the existing AMD CPUs and why they tend to be so far behind Intel in some performance tests. The biggest issue that we have found is in the memory controller. Where the average Intel CPU shows 18-21GB/s worth of bandwidth even AMD’s top of the line Phenom II X6 tops out at between 14-16GB/s. This is a serious issue when you are dealing with multiple CPU cores and applications that are getting more and more bloated. But why is this an issue? One of the reasons is AMD’s caching structure. Back in the days when AMD was on top their memory and cache performance was a key component of this success. Part of this was also due to the extremely low latency of DDR (I can remember buying CAS 1 DDR modules which just flew). Then when the AM2 CPUs came out with reduced cache sizes and their DDR2 controllers (which were little more than the original IMCs improved to support DDR2) the much higher latency had a huge impact on AMD’s performance especially with the smaller cache available to the CPU cores. So while we knew the CPU was improved, the actual performance was negligible.

Moving forward into the Phenom and Phenom II AMD had even more problems with memory performance on these CPUs this was despite them trying to add in more cache (and associations). The issue still revolved around the fact that the IMC for these processors had still not changed much in terms of core design. Nor had the caching structure; sure it had gotten larger but its overall performance had not improved much.

Now for comparison let’s talk about the technology behind each IMC. AMD’s Phenom II has a 144-bit DDR3 controller under the hood which according to AMD should be able to get you up to 21GB/s of memory bandwidth. The fact that we have never seen that is due to the cache structure each CPU core has two 64KB L1 cache blocks (Data and Instruction) 512KB (16-way associative) to work with while the total L3 shared Cache is limited to 6MB (64-way Associative).

Compared to Intel’s Core IMC (dual channel only) the CPU has two 64-bit Memory controllers, which allows their very different caching structure to operate a little more efficiently. Intel’s Core i7 has two levels of L1 cache per core (again Data and Instruction) each are 32KB while the L2 cache is at 256KB per core (only 8-way associative) and the L3 cache is bumped up to 8MB (16-way associative). Now that 8MB is also shared with the IGP that is on the Core i7 and is also stretched by the extra thread per CPU, but the core design allows it to operate in a way that AMD’s just cannot (at this time). There is also a lot to be said for the streamlined instruction in the new Core CPUs as well as the smaller process size.

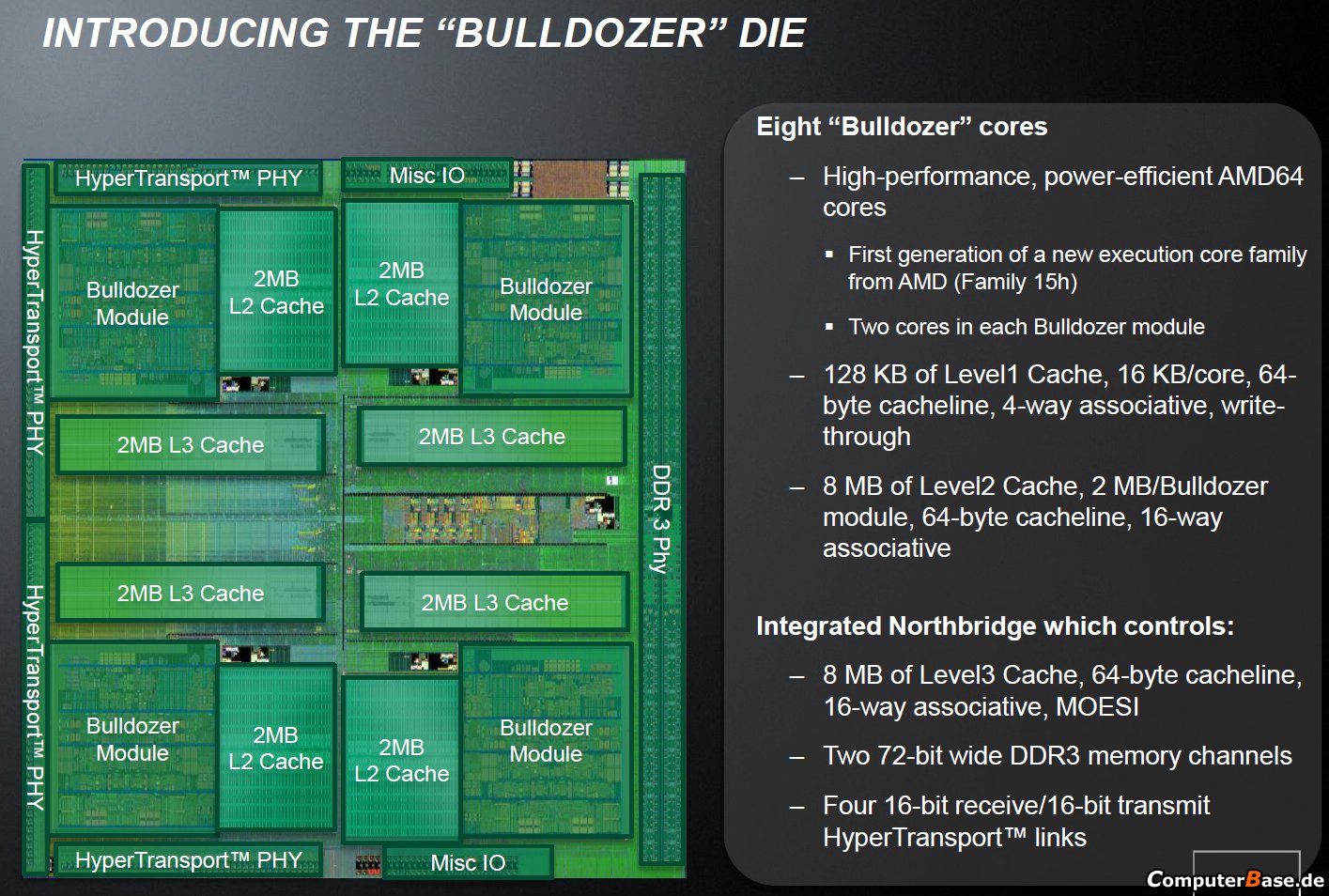

Bulldozer, on the other hand, shows up with two 72-bit wide DDR3 memory controllers (which still add up to 144-bits) this serves four Bulldozer modules (each has two Cores) . The Caching structure is also different you get L1 at 128KB (still broken into two 64 KB blocks), 8MB of L2 Cache (2MB per Bulldozer Module) and 8MB of L3 Cache. Both the L2 and L3 are 16-way associative. The last is interesting as it moves away from the massive 64-way Association that Phenom II had.

Of course we are still only seeing 1MB of L3 per real core, but we might have hope for AMD yet. That is IF these changes to the caching and memory will amount to something. Time will tell on this one as we all know and we all are certainly waiting to see just how this new CPU (the first real new CPU in a long time) from AMD will do. I would love to see this new CPU show that AMD can still produce great products, after all it will only push Intel in making improvements of their own and at that point… the consumer wins.

Image and source ComputerBase.de

Discuss this in our Forum