MIPS Warrior I-class processor cores expand 64-bit processing into embedded, mobile, digital consumer, advanced communications, networking and storage platforms. Their new I-class CPU IP is the first production CPU combining the talents of Imagination’s core developers with MIPS core developers.

MIPS Computer Systems Inc. was founded in 1984 by a group of researchers from Stanford University Since 1991, MIPS have offered a 64-bit instruction set architecture. The original group included Dr. John L. Hennessy who has been president of Stanford since 2000.

|

Tony King-Smith, EVP marketing, Imagination says: “This is the MIPS Warrior core that many have been waiting for. As the industry moves toward instruction set neutrality, customers can now choose a CPU based on its technical superiority. The I6400 is more efficient, flexible and scalable than the competition, and its feature set clearly lends itself to the needs of a wide range of next-generation applications including smartphones and tablets. We know that unique features like multi-threading provide significant advantages for many applications, and customers already using this technology agree. Unsurprisingly, we’ve already secured licensees for the I6400 across multiple markets.”

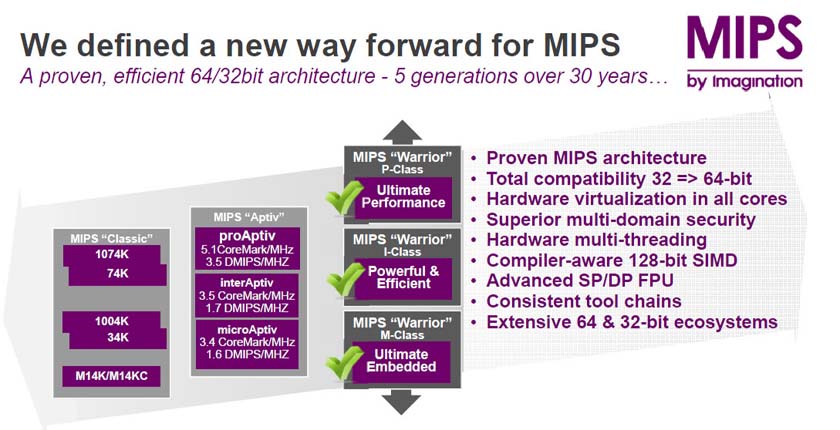

MIPS family of CPUs has a higher CoreMark/MHz than the competition with a smaller amount of the CPU area. Thus, MIPS delivers a superior performance-to-area ratio. MIPS has been deeply involved in developing the Internet of Things (IoT) or Machine-to-Machine (M2M) cloud-connected devices.

Imagination says the I6400 achieves over 50 percent higher CoreMark performance and 30 percent higher DMIPS (Dhrystone MIPS ) compared to leading competitors in its class. MIPS’ note to editors tells us that they are comparing published information from their main competitor (ARM Cortex A-53 / A-57). We shall see what results actually show up when they are compared by published independent benchmarks.

The I6400 will run the upcoming Android “L”, a 64-bit OS. Many operating systems have been ported to MIPS architecture. They are current on one or more of their processor families. This includes Linux and its various distributions. Android has been fully functional on MIPS since spring 2013. Mozilla FireFox and most of the popular RTOS’s from ThreadX to Nucleus to uCOS to Free RTOS run on the MIPS I6400 CPU.

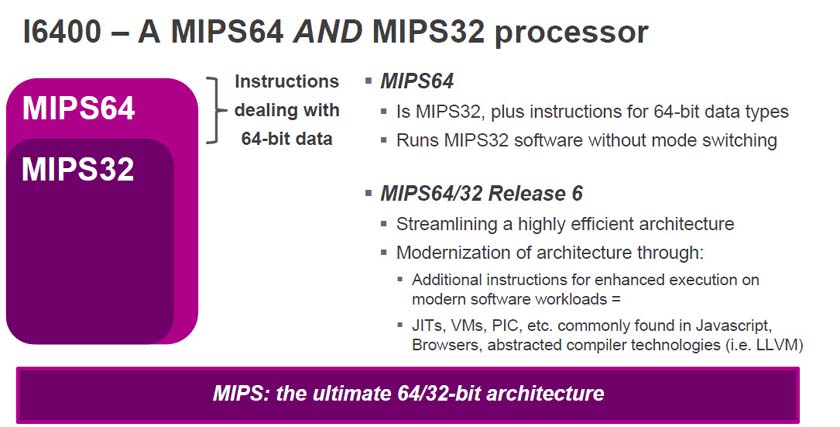

However, not everybody needs a 64-bit CPU for every platform. Thirty-two bit applications will clearly be around for a few more years.

The Warrior I6400 architecture has the big advantage of total compatibility for MIPS32 software without mode switching. This provides developers with the broadest set of applications ever addressed by a single MIPS core family. The MIPS64 ecosystem doesn’t require separate ISAs, data paths or mode switching. Therefore it eliminates wasted silicon area and saves battery power.

|

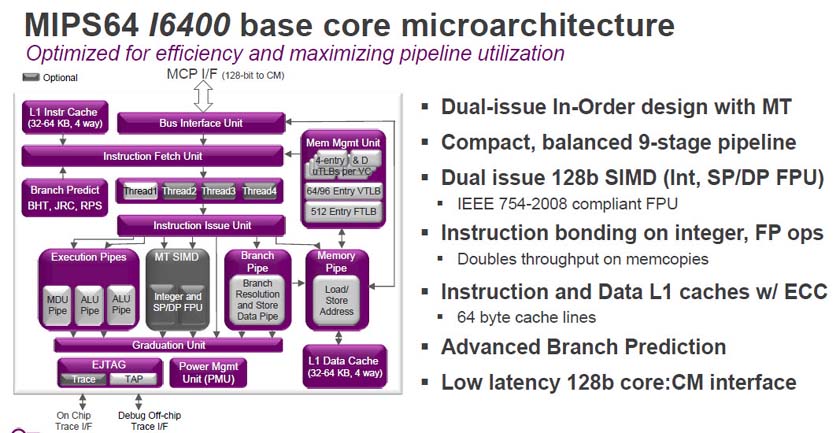

The I6400 is an impressive CPU IP. It provides superscalar in-order execution, simultaneous multi-threading, hardware virtualization, advanced power management, efficient FPU, 128-bit data paths, new multicore coherent interconnect architecture, and a 16-stage pipeline. It gets the full SIMD (single instruction multiple data) treatment and handles both single and double-precision floating-point numbers with ease.

The cores are also designed to operate in heterogeneous clusters in future SoC implementations leveraging CPUs, GPUs and other processing elements. The I6400 handles up to six cores per cluster, and up to 64 clusters, where multiple cores on a single cluster can have different synthesis targets, and operate at different clock frequencies and voltages.

|

I6400 customers benefit from the broad ecosystem that already exists around MIPS, including software, tools and applications and the new prpl open source foundation. The I6400 RTL (register transfer level) IP will begin shipping in December 2014.

Tell us what you think in our Forum